بلوکهای منطقی اصلیترین عنصر در FPGA برای پیاده سازی توابع منطقی از ساده ترین آن تا مدارات پیچیده هستند. این بلوکها در FPGAهای ساخت شرکت Altera نام LAB (Logic Array Block) به خود گرفته است و در تراشه های شرکت Xilinx با نام CLB (configurable logic block) شناخته میشود. از آنجایی که ساختار داخل بلوکهای منطقی در این متن بر اساس FPGAهای خانواده سری 7 و SPARTAN6 توضیح داده میشود از نام CLB استفاده میکنیم.

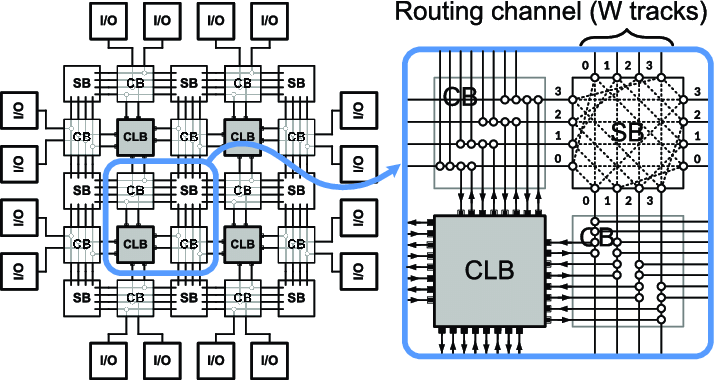

تعداد زیادی بلوک CLB بصورت آرایه ای درون FPGA قرار دارند. هر CLB به یک ماتریس سوئیچ برای ایجاد ارتباط با سایر منابع موجود در FPGA متصل است.

آرایه CLBها در FPGA و نحوه ارتباط آنها

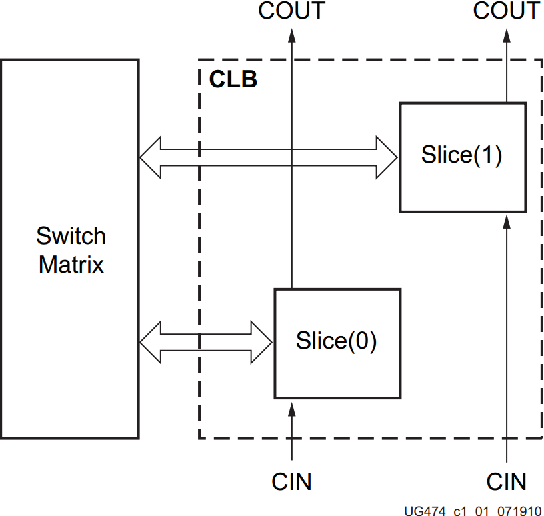

معماری داخلی CLBها در برخی خانواده های Xilinx متفاوت است. در سری 6 و7 FPGAها، CLBها متشکل از دو اسلایس هستند که در دو ستون قرار دارند. ورودی و خروجی های این دو اسلایس به ماتریس سوئیچ متصل میشوند و بطور مستقیم به یکدیگر متصل نیستند.

چینش اسلایسها در یک CLB

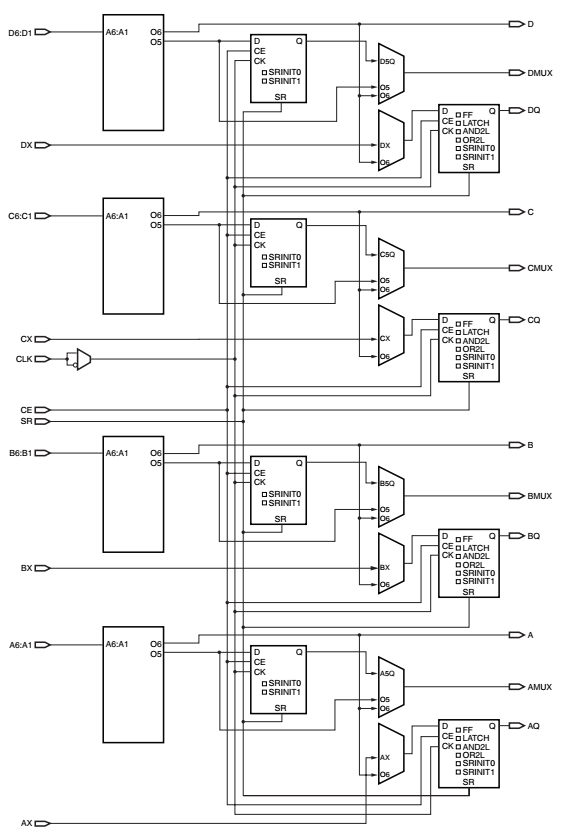

اسلایسهای موجود در بلوکهای قابل پیکره بندی در خانواده SPARTAN6 شامل سه نوع SLICEX, SLICEL و SLICEM است. در حالی که در خانواده سری 7 فقط از انواع SLICEL و SLICEM استفاده شده است. SLICEX ساده ترین نوع اسلایسها است. و فقط شامل ۴ عدد LUT شش ورودی، ۸ عدد فلیپ فلاپ است. در مورد LUTها و ساختار آنها در ادامه توضیحاتی ارائه میگردد.

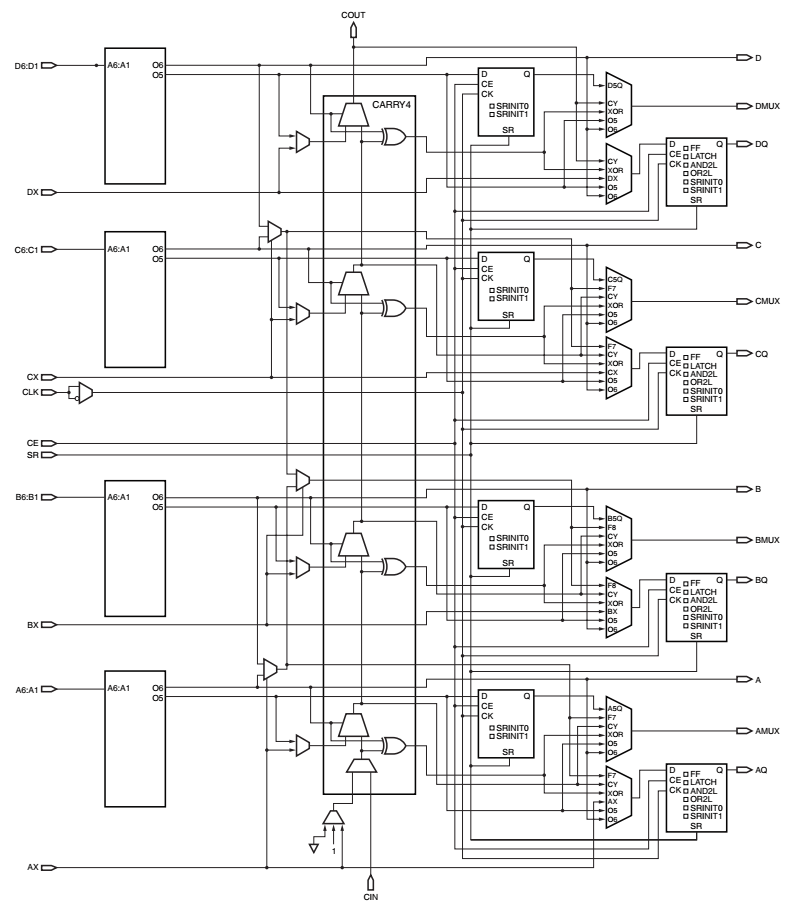

معماری داخل SliceX

در SLICELها علاوه بر LUT و فلیپ فلاپ های موجود در SLICEX، یک مدار زنجیره بیت نقلی یا CARRY نیز به آن افزوده شده است. این مدار در پیاده سازی بهینه طراحی های سخت افزاری مانند جمع کننده ها یا شمارنده ها بسیار موثر است. همچنین این اسلایسها شامل مالتی پلکسرهایی هستند که کمک میکنند توابع با ورودی های بیشتر از 6 را نیز بتوان پیاده سازی نمود به همین دلیل آنها را مالتی پلکسرهای عریض نامگذاری کردند.

معماری داخل SliceL

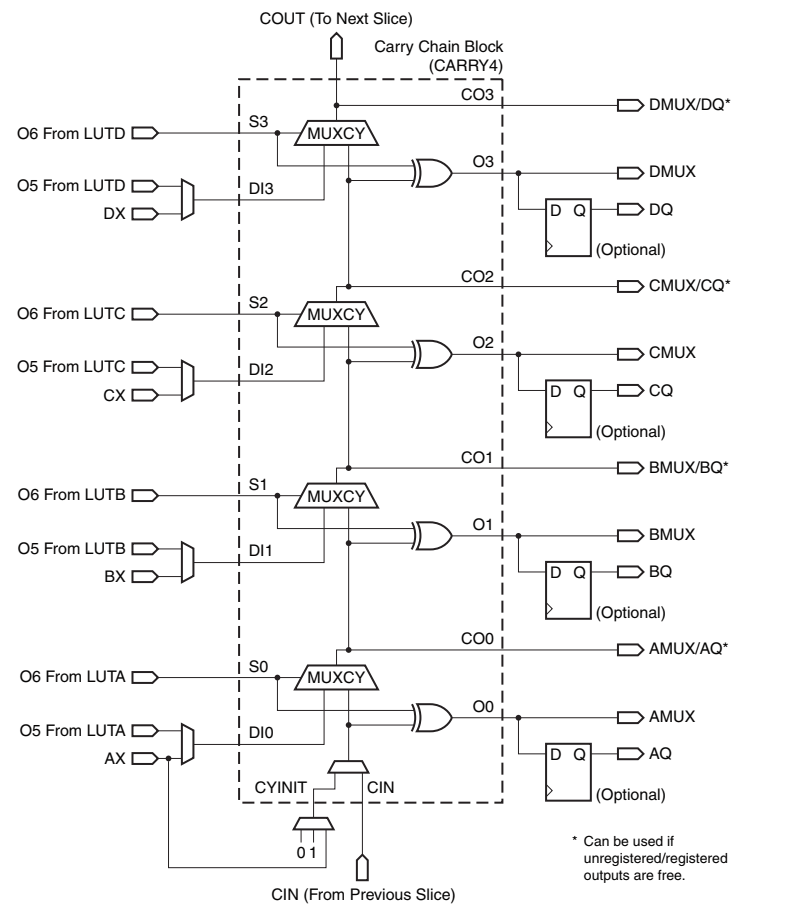

زنجیره بیت نقلی در یک اسلایس تنها چهار بیت ارتفاع دارد و مداری است که مستقیماً ستونی از اسلایس ها را به هم متصل می کند. این امکان وجود دارد که یک زنجیره نقلی را در چندین اسلایس ستونی به منظور اجرای سریع عملیات هایی که برای پردازش به بیش از یک اسلایس احتیاج دارند بصورت آبشاری به هم متصل کرد.

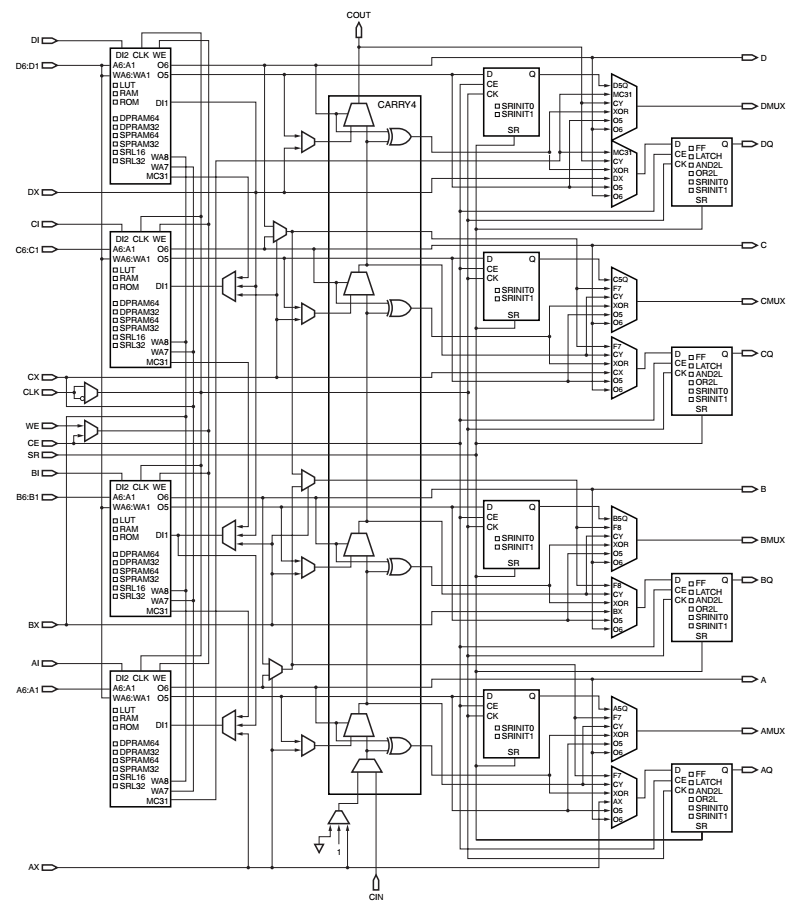

SLICEMها همانند SLICELها از LUTها و فلیپ فلاپها و مدارهای انتقال بیت نقلی و مالتی پلکسرهای گسترش دهنده بهره میبرند تفاوت SLICEMها در امکانی است که در LUT های آن فراهم شده است. به این صورت که می توان از آنها بعنوان حافظه های RAM توزیع شده 64 بیتی یا شیفت رجیستر استفاده کرد.

معماری داخل SliceM

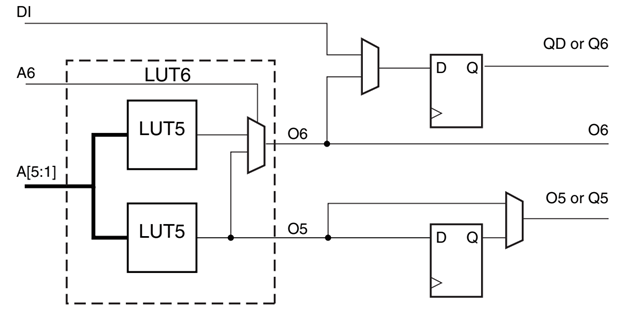

همانطور که گفته شد LUT ها بلوکهای اصلی برای پیاده سازی عملیاتها و توابع منطقی هستند. به این شکل که جدول صحت هر تابع منطقی بسته به ورودی ها دارای یک خروجی مطلوب میباشد. هنگام پیادهسازی یک تابع ، جدول درستی این تابع براساس کد نوشته شده توسط کاربر، توسط ابزار سنتز کد استخراج میشود. سپس مقادیر این جدول صحت در هنگام پیکره بندی تراشه در خانه های حافظه LUT ها مقداردهی میشود. LUTهای درون اسلایس ها در خانواده سری 6 و 7 بصورت 6 ورودی هستند. که در واقع از دو LUT 5 ورودی ساخته شده است. مزیت این معماری این است که به کاربر این امکان را میدهد که از LUT برای پیاده سازی یک عملیات با 6 ورودی و یک خروجی استفاده نماید یا توابعی با 5 ورودی و دو خروجی را نیز در یک LUT تحقق ببخشد.

معماری داخل یک LUT6 که از دو LUT5 تشکیل شده است

در انجام عملیات ریاضی تاثیر زنجیره بیت نقلی در افزایش کارایی مدار بسیار چشمگیر است. زنجیره بیت نقلی در طول یک ستون مستقیما به یکدیگر متصل میشود و این امکان را فراهم میکند تا جمع – تفریق کننده های بزرگتری را بتوان پیاده سازی کرد. زنجیره بیت نقلی به سمت بالا منتقل میشود و در هر اسلایس به اندازه چهار بیت است که با انتقال به اسلایسهای بعدی در CLBهای مجاور به هر تعداد بیت مورد نیاز قابل گسترش است. در مدار زنجیره بیت نقلی، هر بیت شامل یک مالتی پلکسر انتقال (MUXCY) و یک گیت XOR اختصاصی است که شرایط لازم برای انتخاب بیت نقلی در عملیات جمع/ تفریق فراهم میکند.

مدار زنجیره بیت نقلی در یک اسلایس که به اندازه 4 بیت ارتفاع دارد

حال توضیح اینکه این مدار چگونه در افزایش کارایی پیاده سازی جمع/تفریق کننده ها موثر است، در کلمه کلیدی مسیرهای بحرانی نهفته است. مسیرهای بحرانی به طولانیترین مسیرهای موجود در سخت افزار پیاده سازی شده روی تراشه اطلاق میشود. مسیرهای طولانی در مدار باعث افزایش تاخیر و کاهش سرعت و کارایی مدار میشوند. در بحث خاص جمع/تفریق کننده ها مسیر بحرانی و گلوگاه طراحی همان مسیر انتقال بیت نقلی است. هرچه پهنای بیت در عملیات ریاضی مورد نظر بیشتر باشد این تاخیر افزایش می یابد. به وسیله مدار زنجیره بیت نقلی هر تعداد LUT که به صورت ستونی زیر هم قرار گرفته اند، برای پیاده سازی عملیات ریاضی مورد نظر بصورت مستقیم به هم متصل شده و برای انتقال بیت نقلی استفاده می شود. حال اگر این مدار در ساختار اسلایسها وجود نداشت جهت تولید cout باید از LUTها و انتقال آن از مسیر ارتباطی عمومی و از طریق ماتریس سوئیچ استفاده می شد، که در نتیجه آن تاخیر نقلی خروجی ناشی از LUTها بعلاوه مسیرهای routing مورد نیاز برای برقراری ارتباط بین آن ها بسیار زیاد می شد و با افزایش تعداد بیت ها کارایی مدار به شدت افت می کرد.

در این بخش تا حدودی با معماری درون CLBها آشنا شدیم هر چند در ابتدای شروع کار با FPGA، عدم اطلاع از معماری CLBها خدشه ای در طراحی و پیاده سازی مدار وارد نمی کند. و بسیاری از کارهای مربوط به پیاده سازی مدار در این بلوکها توسط ابزار سنتز انجام میشود و از دید طراح پنهان است. لیکن در زمانی که محدودیت های منابع مصرفی و سرعت وجود دارد برای استفاده بهینه از معماری موجود در CLBها مفید خواهد بود.